# Parallel Programming An Introduction

### Xu Liu

Derived from Prof. John Mellor-Crummey's COMP 422 from Rice University

# Applications need performance (speed)

## **The Need for Speed: Complex Problems**

- Science

- -storm forecasting and climate prediction

- Engineering

- -combustion and engine design

- -computational fluid dynamics and airplane design

- -earthquake and structural modeling

- -pollution modeling and remediation planning

- -molecular nanotechnology

- Business

- -computational finance high frequency trading

- —information retrieval

- -data mining

- Defense

- -nuclear weapons stewardship

- -cryptology

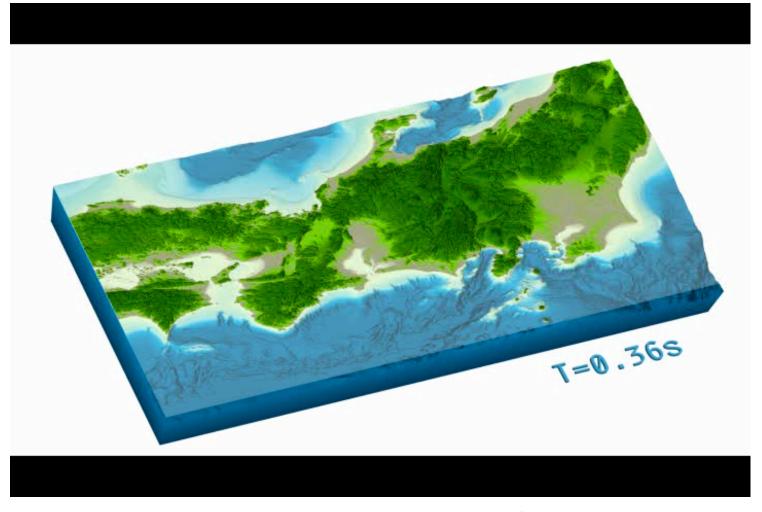

### **Earthquake Simulation**

Earthquake Research Institute, University of Tokyo Tonankai-Tokai Earthquake Scenario Photo Credit: The Earth Simulator Art Gallery, CD-ROM, March 2004

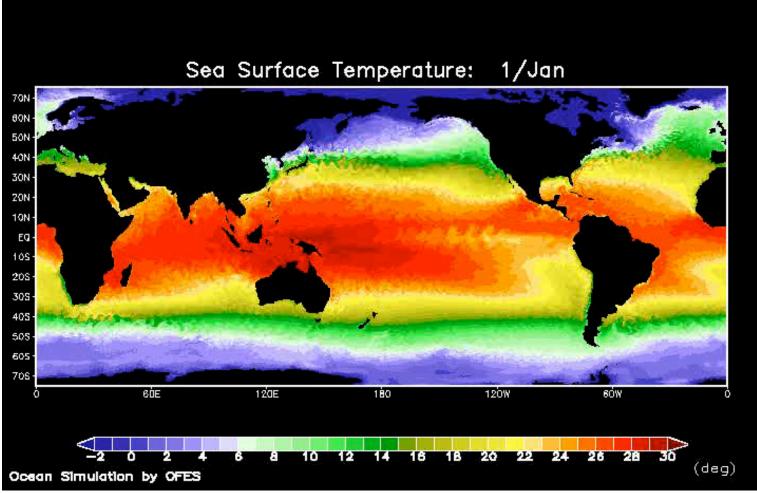

### **Ocean Circulation Simulation**

Ocean Global Circulation Model for the Earth Simulator Seasonal Variation of Ocean Temperature Photo Credit: The Earth Simulator Art Gallery, CD-ROM, March 2004

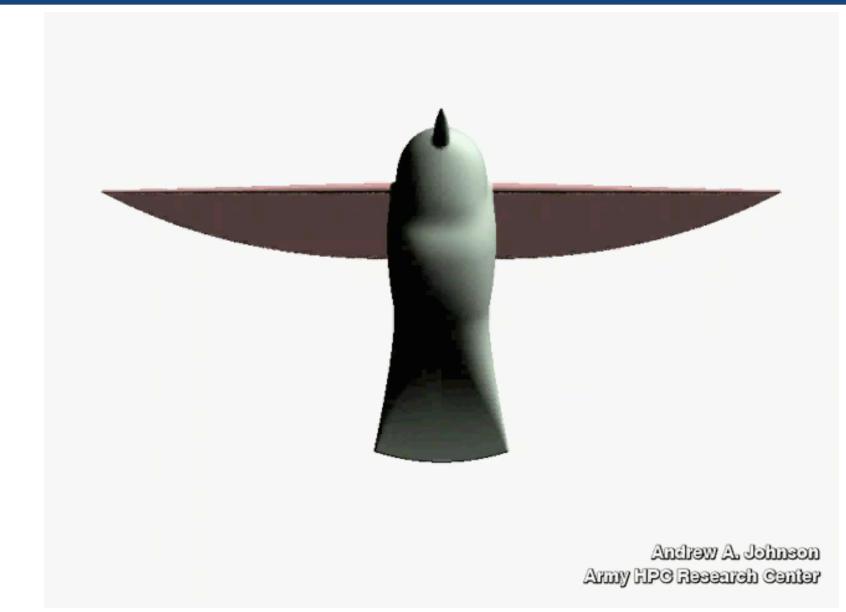

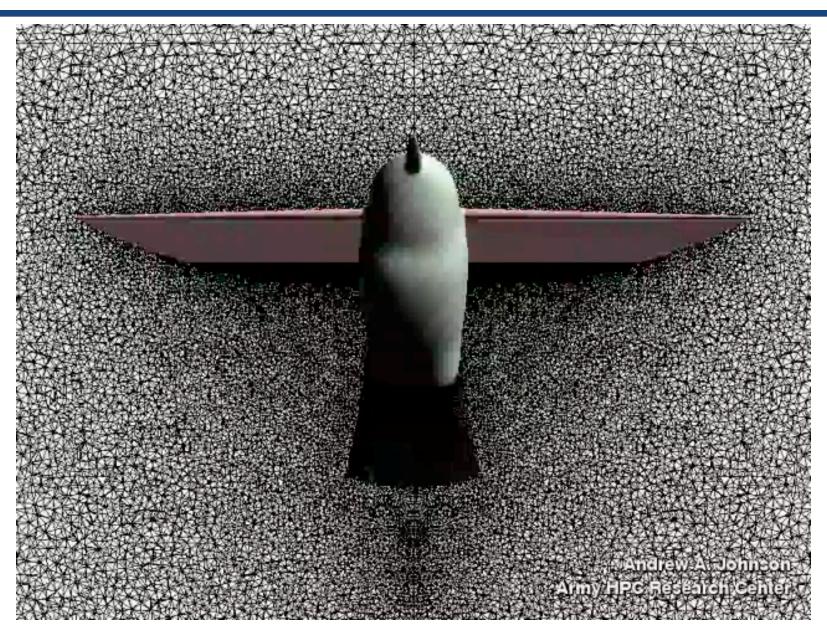

## **Air Velocity (Front)**

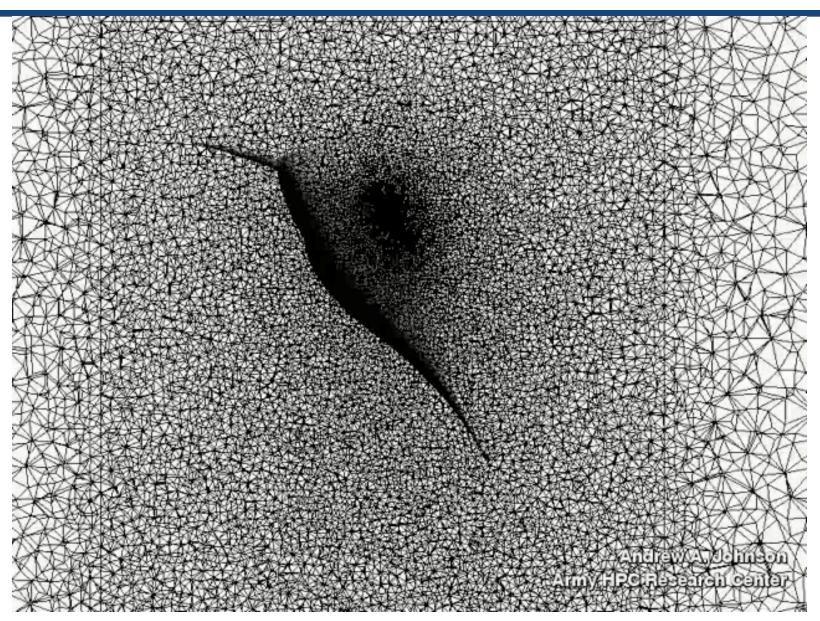

### Air Velocity (Side)

## **Mesh Adaptation (front)**

### **Mesh Adaptation (side)**

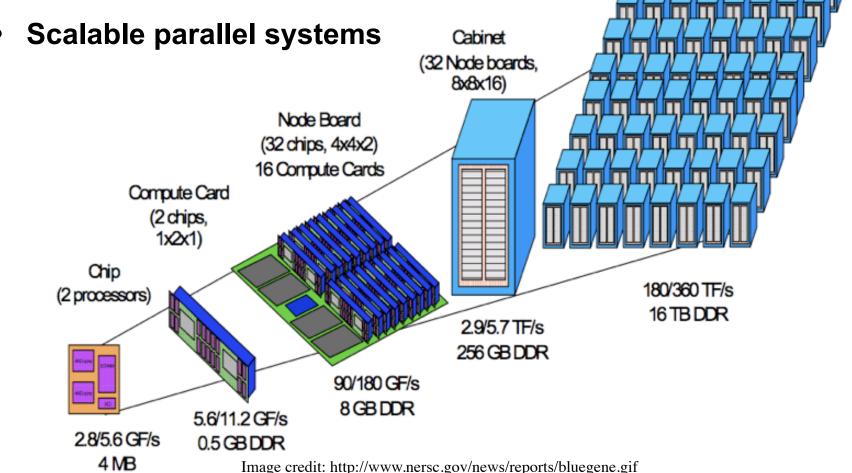

# Parallel Hardware in the Large

### **Hierarchical Parallelism in Supercomputers**

System

(64 cabinets, 64x32x32)

- Cores with pipelining and short vectors

- Multicore processors

- Shared-memory multiprocessor nodes

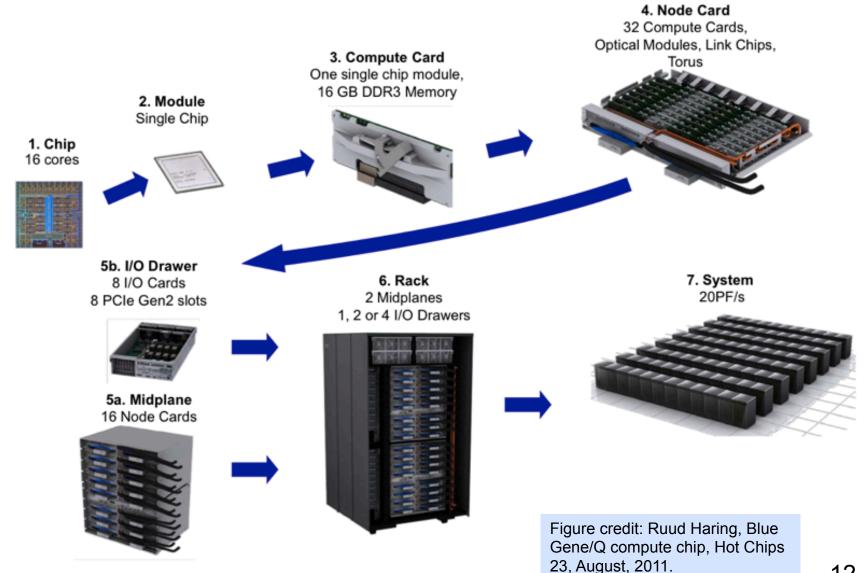

## **Blue Gene/Q Packaging Hierarchy**

### Scale of the Largest HPC Systems (Nov 2013)

| Rank | Site                                                                  | System                                                                                                                      | Cores     | Rmax<br>(TFlop/s) | Rpeak<br>(TFlop/s) | Power<br>(kW) | > 1.5M            |

|------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------|-------------------|--------------------|---------------|-------------------|

| 0    | National Super Computer Center<br>in Guangzhou<br>China               | Tianhe-2 (MilkyWay-2) - TH-IVB-FEP Cluster, Intel Xeon E5-<br>2692 12C 2.200GHz, TH Express-2, Intel Xeon Phi 31S1P<br>NUDT | 3,120,000 | 33,862.7          | 54,902.4           | 17,808        | cores             |

| 2    | DOE/SC/Oak Ridge National<br>Laboratory<br>United States              | Titan - Cray XK7 , Opteron 6274 16C 2.200GHz, Cray Gemini<br>interconnect, NVIDIA K20x<br>Cray Inc.                         | 560,640   | 17,590.0          | 27,112.5           | 8,209         |                   |

| 3    | DOE/NNSA/LLNL<br>United States                                        | Sequoia - BlueGene/Q, Power BQC 16C 1.60 GHz, Custom IBM                                                                    | 1,572,864 | 17,173.2          | 20,132.7           | 7,890         | all               |

| 4    | RIKEN Advanced Institute for<br>Computational Science (AICS)<br>Japan | K computer, SPARC64 VIIIfx 2.0GHz, Tofu interconnect<br>Fujitsu                                                             | 705,024   | 10,510.0          | 11,280.4           | 12,660        | > 100K<br>cores   |

| 5    | DOE/SC/Argonne National<br>Laboratory<br>United States                | Mira - BlueGene/Q, Power BQC 16C 1.60GHz, Custom<br>IBM                                                                     | 786,432   | 8,586.6           | 10,066.3           | 3,945         |                   |

| 6    | Swiss National Supercomputing<br>Centre (CSCS)<br>Switzerland         | Piz Daint - Cray XC30, Xeon E5-2670 8C 2.600GHz, Aries<br>interconnect , NVIDIA K20x<br>Cray Inc.                           | 115,984   | 6,271.0           | 7,788.9            | 2,325         | hybrid<br>CPU+GPU |

| 7    | Texas Advanced Computing<br>Center/Univ. of Texas<br>United States    | Stampede - PowerEdge C8220, Xeon E5-2680 8C 2.700GHz,<br>Infiniband FDR, Intel Xeon Phi SE10P<br>Dell                       | 462,462   | 5,168.1           | 8,520.1            | 4,510         |                   |

| 8    | Forschungszentrum Juelich (FZJ)<br>Germany                            | JUQUEEN - BlueGene/Q, Power BQC 16C 1.600GHz, Custom<br>Interconnect<br>IBM                                                 | 458,752   | 5,008.9           | 5,872.0            | 2,301         |                   |

| 9    | DOE/NNSA/LLNL<br>United States                                        | Vulcan - BlueGene/Q, Power BQC 16C 1.600GHz, Custom<br>Interconnect<br>IBM                                                  | 393,216   | 4,293.3           | 5,033.2            | 1,972         |                   |

| 10   | Leibniz Rechenzentrum<br>Germany                                      | SuperMUC - iDataPlex DX360M4, Xeon E5-2680 8C 2.70GHz,<br>Infiniband FDR                                                    | 147,456   | 2,897.0           | 3,185.1            | 3,423         | 13                |

### **Top Petascale Systems**

### (PetaFLOPS = 10<sup>15</sup> FLoating-point Operations Per Second)

- China: NUDT Tianhe-1a

- -hybrid architecture

- 14,336 6-core Intel Westmere processors

- 7,168 NVIDIA Tesla M2050M GPU

- -proprietary interconnect

- —peak performance ~4.7 petaflop

- ORNL Jaguar system

- -over 224K processor cores

- -toroidal interconnect topology: Cray Seastar2+

- —peak performance ~2.3 petaflop

- -upgraded 2009

14

# **Challenges of Parallelism in the Large**

- Parallel science applications are often very sophisticated — e.g. adaptive algorithms may require dynamic load balancing

- Multilevel parallelism is difficult to manage

- Extreme scale exacerbates inefficiencies

- algorithmic scalability losses

- serialization and load imbalance

- communication or I/O bottlenecks

- insufficient or inefficient parallelization

- Hard to achieve top performance even on individual nodes

- contention for shared memory bandwidth

- memory hierarchy utilization on multicore processors

Parallel Programming Concept

### **Decomposing Work for Parallel Execution**

- Divide work into tasks that can be executed concurrently

- Many different decompositions possible for any computation

- Tasks may be same, different, or even indeterminate sizes

- Tasks may be independent or have non-trivial order

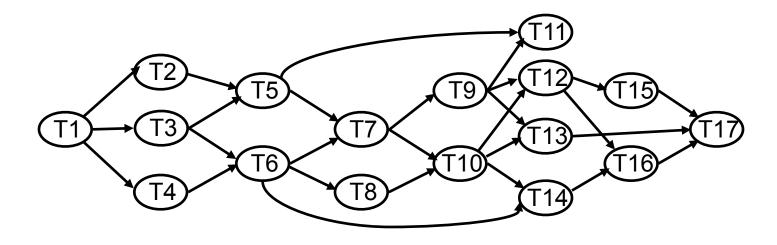

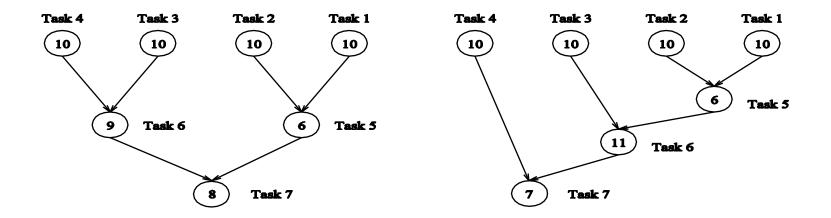

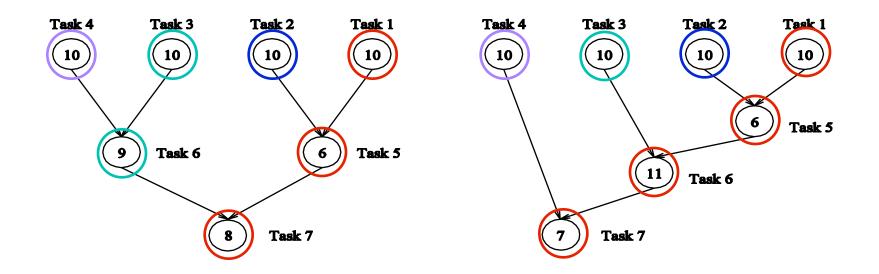

- Conceptualize tasks and ordering as *task dependency DAG* —node = task

- —edge = control dependence

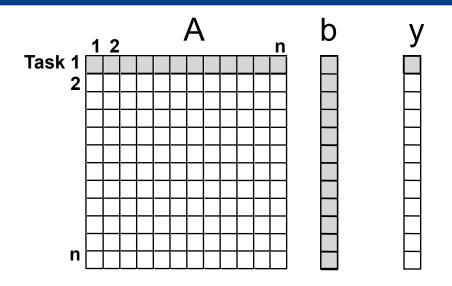

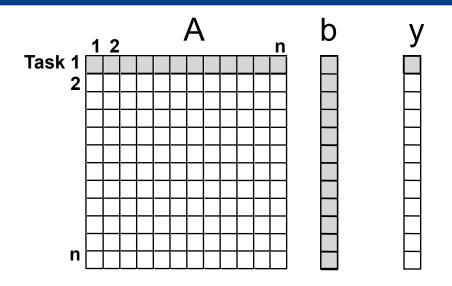

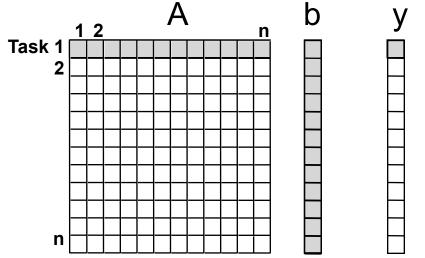

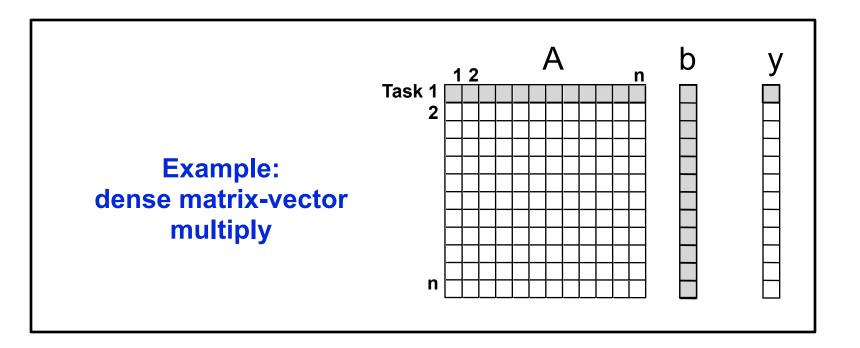

## **Example: Dense Matrix-Vector Multiplication**

- Computing each element of output vector y is independent

- Easy to decompose dense matrix-vector product into tasks —one per element in y

- Observations

- -task size is uniform

- -no control dependences between tasks

- -tasks share b

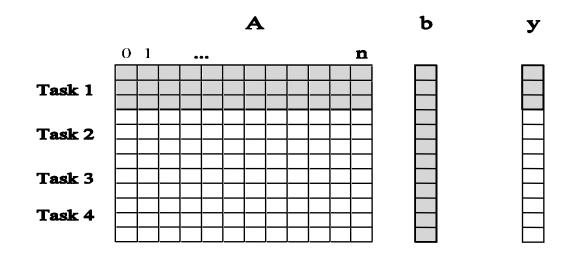

### **Granularity of Task Decompositions**

Granularity = task size

-depends on the number of tasks

- Fine-grain = large number of tasks

- Coarse-grain = small number of tasks

- Granularity examples for dense matrix-vector multiply

- fine-grain: each task represents an individual element in y

coarser-grain: each task computes 3 elements in y

### **Degree of Concurrency**

- Definition: number of tasks that can execute in parallel

- May change during program execution

- Metrics

- *—maximum degree of concurrency*

- largest # concurrent tasks at any point in the execution

- *—average degree of concurrency*

- average number of tasks that can be processed in parallel

- Degree of concurrency vs. task granularity

—inverse relationship

## **Example: Dense Matrix-Vector Multiplication**

- Computing each element of output vector y is independent

- Easy to decompose dense matrix-vector product into tasks —one per element in y

- Observations

- -task size is uniform

- -no control dependences between tasks

- -tasks share b

Question: Is *n* the maximum number of tasks possible? 21

### **Critical Path**

- Edge in task dependency graph represents task serialization

- Critical path = longest weighted path though graph

- Critical path length = lower bound on parallel execution time

### **Critical Path Length**

#### **Questions:**

What are the tasks on the critical path for each dependency graph? What is the shortest parallel execution time for each decomposition? How many processors are needed to achieve the minimum time? What is the maximum degree of concurrency? What is the average parallelism? Example: dependency graph for dense-matrix vector product

#### **Questions:**

- What does a task dependency graph look like for DMVP?

- What is the shortest parallel execution time for the graph?

- How many processors are needed to achieve the minimum time?

- What is the maximum degree of concurrency?

- What is the average parallelism?

### **Limits on Parallel Performance**

- What bounds parallel execution time?

- - e.g. dense matrix-vector multiplication ≤ n<sup>2</sup> concurrent tasks

- -dependencies between tasks

- -parallelization overheads

- e.g., cost of communication between tasks

- -fraction of application work that can't be parallelized

- Amdahl's law

- Measures of parallel performance

- -speedup =  $T_1/T_p$

- -parallel efficiency = T<sub>1</sub>/(pT<sub>p</sub>)

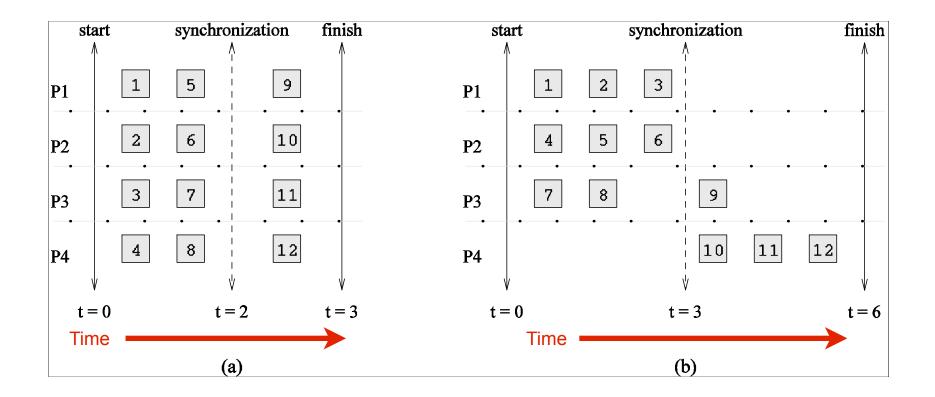

## **Processes and Mapping Example**

- Consider the dependency graphs in levels —no nodes in a level depend upon one another —compute levels using topological sort

- Assign all tasks within a level to different processes

# Task Decomposition

### **Decomposition Based on Output Data**

- If each element of the output can be computed independently

- Partition the output data across tasks

- Have each task perform the computation for its outputs

### **Output Data Decomposition: Example**

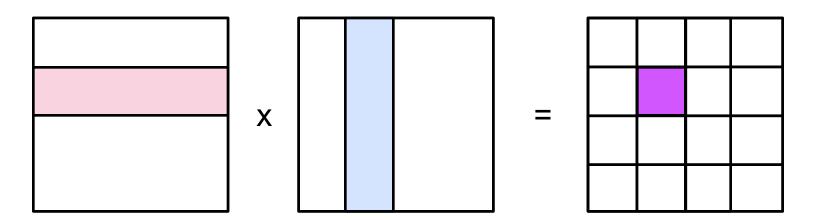

- Matrix multiplication:  $C = A \times B$

- Computation of C can be partitioned into four tasks

$$\begin{pmatrix} A_{1,1} & A_{1,2} \\ A_{2,1} & A_{2,2} \end{pmatrix} \cdot \begin{pmatrix} B_{1,1} & B_{1,2} \\ B_{2,1} & B_{2,2} \end{pmatrix} \to \begin{pmatrix} C_{1,1} & C_{1,2} \\ C_{2,1} & C_{2,2} \end{pmatrix}$$

$$\begin{array}{ll} {\rm Task \ 1:} & C_{1,1} = A_{1,1}B_{1,1} + A_{1,2}B_{2,1} \\ {\rm Task \ 2:} & C_{1,2} = A_{1,1}B_{1,2} + A_{1,2}B_{2,2} \\ {\rm Task \ 3:} & C_{2,1} = A_{2,1}B_{1,1} + A_{2,2}B_{2,1} \\ {\rm Task \ 4:} & C_{2,2} = A_{2,1}B_{1,2} + A_{2,2}B_{2,2} \end{array}$$

#### Other task decompositions possible

### **Exploratory Decomposition**

- Exploration (search) of a state space of solutions

—problem decomposition reflects shape of execution

- Examples

- -theorem proving

- -game playing

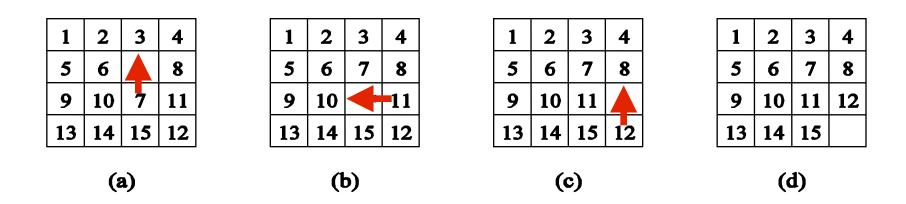

### **Exploratory Decomposition Example**

### Solving a 15 puzzle

• Sequence of three moves from state (a) to final state (d)

• From an arbitrary state, must search for a solution

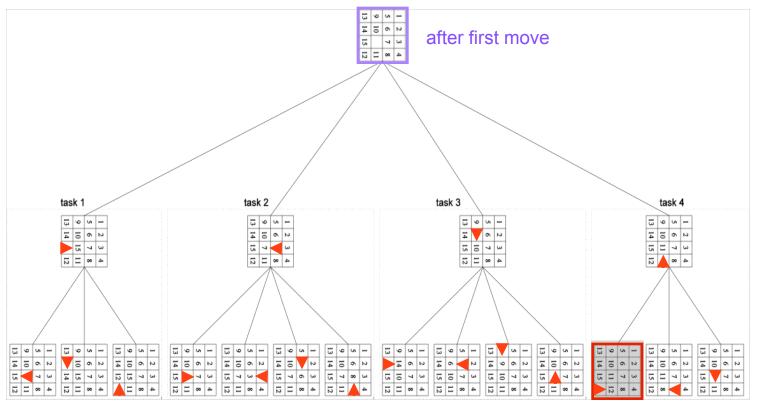

### **Exploratory Decomposition: Example**

### Solving a 15 puzzle

### Search

#### -generate successor states of the current state

-explore each as an independent task

# **Task Mapping**

## **Mapping Techniques**

### Map concurrent tasks to processes for execution

- Overheads of mappings

- -serialization (idling)

- -communication

- Select mapping to minimize overheads

- Conflicting objectives: minimizing one increases the other

- -assigning all work to one processor

- minimizes communication

- significant idling

# **Mapping Techniques for Minimum Idling**

- Must simultaneously minimize idling and load balance

- Balancing load alone does not minimize idling

# **Mapping Techniques for Minimum Idling**

### Static vs. dynamic mappings

- Static mapping

- *—a-priori* mapping of tasks to processes

- -requirements

- a good estimate of task size

- Dynamic mapping

- -map tasks to processes at runtime

- —why?

- tasks are generated at runtime, or

- their sizes are unknown

### Factors that influence choice of mapping

- size of data associated with a task

- nature of underlying domain

### **Schemes for Static Mapping**

- Data partitionings

- Task graph partitionings

- Hybrid strategies

### **Mappings Based on Data Partitioning**

#### Partition computation using a combination of

- -data partitioning

- -owner-computes rule

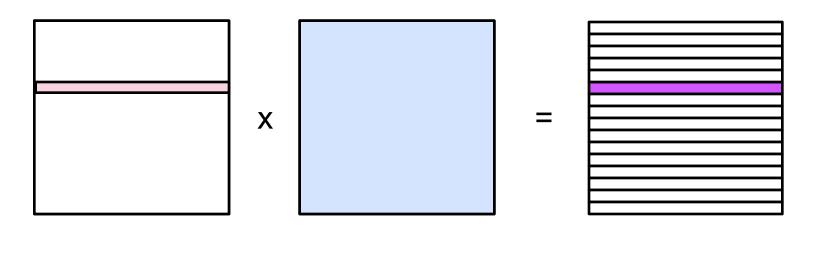

#### **Example: 1-D block distribution for dense matrices**

row-wise distribution

column-wise distribution

### **Block Array Distribution Schemes**

### **Multi-dimensional block distributions**

#### **Multi-dimensional partitioning enables larger # of processes**

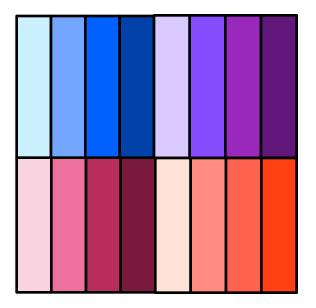

### **Data Usage in Dense Matrix Multiplication**

#### Multiplying two dense matrices C = A x B

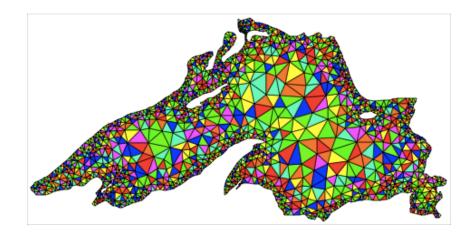

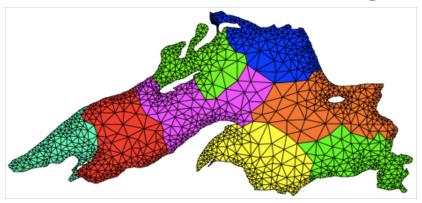

### **Partitioning a Graph of Lake Superior**

#### **Random Partitioning**

#### Partitioning for minimum edge-cut

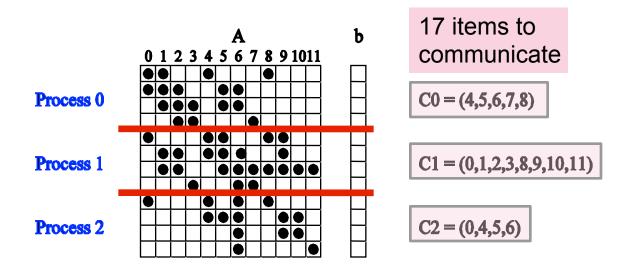

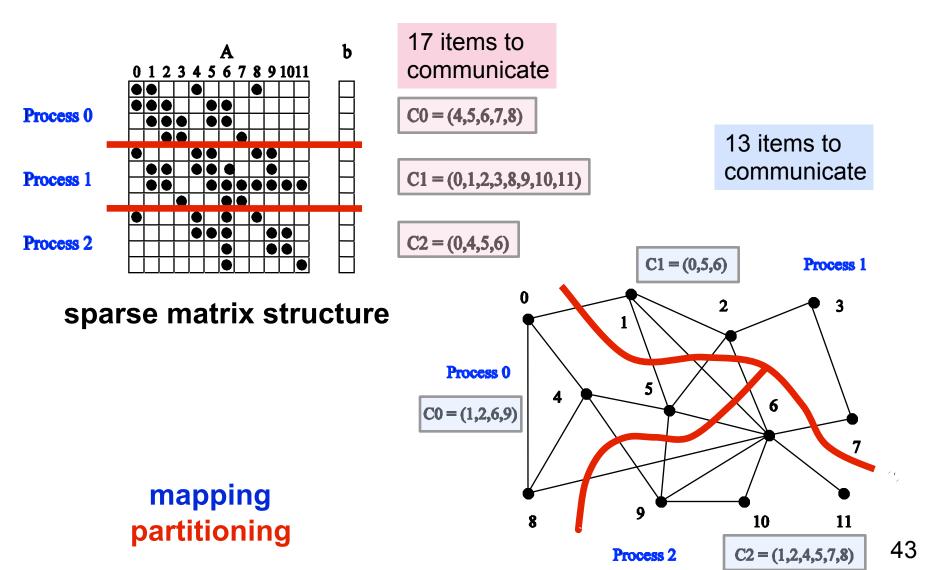

### Mapping a Sparse Matrix

#### **Sparse matrix-vector product**

sparse matrix structure

mapping partitioning

1

### Mapping a Sparse Matrix

#### **Sparse matrix-vector product**

# **Schemes for Dynamic Mapping**

• Dynamic mapping AKA dynamic load balancing

—load balancing is the primary motivation for dynamic mapping

- Styles

- -centralized

- -distributed

## **Centralized Dynamic Mapping**

- Processes = masters or slaves

- General strategy

—when a slave runs out of work  $\rightarrow$  request more from master

• Challenge

—master may become bottleneck for large # of processes

- Approach

- -chunk scheduling: process picks up several of tasks at once

- -however

- large chunk sizes may cause significant load imbalances

- gradually decrease chunk size as the computation progresses

## **Distributed Dynamic Mapping**

- All processes as peers

- Each process can send or receive work from other processes —avoids centralized bottleneck

- Four critical design questions

- -how are sending and receiving processes paired together?

- -who initiates work transfer?

- —how much work is transferred?

- —when is a transfer triggered?

- Ideal answers can be application specific

- Cilk uses a distributed dynamic mapping: "work stealing"

# **Minimizing Interaction Overheads (1)**

#### "Rules of thumb"

- Minimize volume of data exchange

- -partition interaction graph to minimize edge crossings

- Minimize frequency of communication

-try to aggregate messages where possible

- Minimize contention and hot-spots

# **Minimizing Interaction Overheads (2)**

### **Techniques**

- Overlap communication with computation

- -use non-blocking communication primitives

- overlap communication with your own computation

- one-sided: prefetch remote data to hide latency

- -multithread code on a processor

- overlap communication with <u>another thread's</u> computation

- Replicate data or computation to reduce communication

- Use group communication instead of point-to-point primitives

- Issue multiple communications and overlap their latency (reduces exposed latency)